# MOS INTEGRATED CIRCUIT $\mu$ PD16641

# SOURCE DRIVER FOR 240-OUTPUT TFT-LCD (64 GRAY SCALES)

#### **DESCRIPTION**

The  $\mu$ PD16641 is a source driver for TFT-LCD 64 gray scale displays. Its logic circuit operates at 3.3 V and the driver circuit operates at 3.3 or 5.0 V (selectable). The input data is digital data at 6 bits  $\times$  3 dots, and 260,000 colors can be displayed in 64-value outputs  $\gamma$ -corrected by the internal D/A converter and 11 external power supplies.

Because the clock frequency is 33 MHz<sub>MIN</sub>, the  $\mu$ PD16641 can be used in TFT-LCD panels conforming to the VGA standards.

#### **FEATURES**

- · Precharge-less output buffer

- 64-value output by 11 external power supplies and internal D/A converter

- Level of γ-corrected power supply can be inverted

- Output voltage range: 2.8 VP-PMAX. (at supply voltage VDD2 of driver circuit = 3.0 V)

- 4.3 VP-PMAX. (at supply voltage VDD2 of driver circuit = 4.5 V)

- · CMOS level input

- 6 bit (gray scale data) × 3 dot input

- High-speed data transfer: fmax. = 33 MHzmin. (internal data transfer rate at supply voltage Vdd1 of logic circuit = 3.0 V)

- 240 outputs

- Supply voltage of driver circuit selectable (Vsel = H: 3.3 V, Vsel = L: 5.0 V)

- Slim TCP

#### ORDERING INFORMATION

| Part No.      | Package           |

|---------------|-------------------|

| μPD16641N-××× | TCP (TAB package) |

The TCP is custom-made. For details, consult NEC

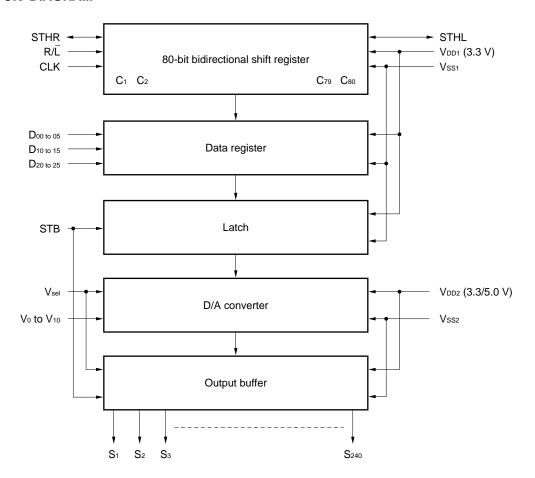

## 1. BLOCK DIAGRAM

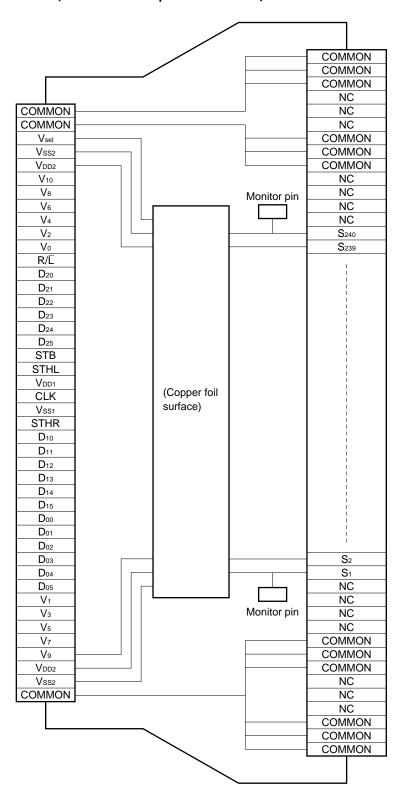

#### 2. PIN CONFIGURATION (standard TCP: $\mu$ PD16641N-xxx)

$\ensuremath{V_{\text{sel}}}$  pin is internally pulled up.

Therefore, the number of input pins can be reduced by opening or short-circuiting these pins to Vss2 by means of TCP wiring.

#### 3. PIN DESCRIPTION

| Pin Symbol                         | Pin Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S <sub>1</sub> to S <sub>240</sub> | Driver output                | Output 64 gray scale analog voltages converted from digital signals.                                                                                                                                                                                                                                                                                                                                                                                      |

| D <sub>00</sub> to D <sub>05</sub> | Display data input           | Inputs 18-bit-wide display gray scale data (6 bits) × 3 dots (RGB).                                                                                                                                                                                                                                                                                                                                                                                       |

| D <sub>10</sub> to D <sub>15</sub> |                              | Dxo: LSB, Dxs: MSB                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D <sub>20</sub> to D <sub>25</sub> |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R/L                                | Shift direction select input | This pin inputs/outputs start pulses when two or more $\mu$ PD16641s are connected in cascade. Shift direction of shift register is as follows: $R/\overline{L}=H: \ STHR \ input, \ S_1 \rightarrow S_{240}, \ STHL \ output$ $R/\overline{L}=L: \ STHL \ input, \ S_{240} \rightarrow S_1, \ STHR \ output$                                                                                                                                             |

| STHR                               | Right shift start pulse I/O  | R/L = H: Inputs start pulse.<br>R/L = L: Outputs start pulse.                                                                                                                                                                                                                                                                                                                                                                                             |

| STHL                               | Left shift start pulse I/O   | $R/\overline{L} = H$ : Outputs start pulse.<br>$R/\overline{L} = L$ : Inputs start pulse.                                                                                                                                                                                                                                                                                                                                                                 |

| Vsel                               | Driver voltage selection     | Selects driver voltage. This pin is internally pulled up to V <sub>DD2</sub> . $V_{\text{sel}} = V_{\text{DD2}} \text{ or OPEN: } V_{\text{DD2}} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{\text{sel}} = \text{L: } V_{\text{DD2}} = 5.0 \text{ V} \pm 0.5 \text{ V}$                                                                                                                                                                                         |

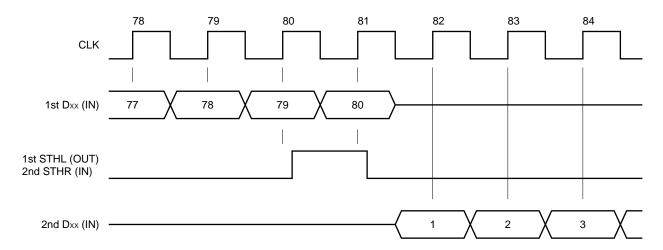

| CLK                                | Shift clock input            | Inputs shift clock to shift register. Display data is loaded to data register at rising edge of this pin.  Start pulse output goes high at rising edge of 80th clock after start pulse has been input, and serves as start pulse to driver in next stage. 80th clock of driver in first stage serves as start pulse of driver in next stage.                                                                                                              |

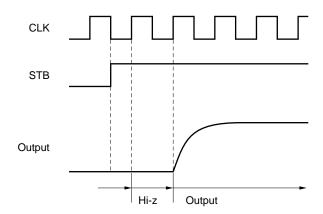

| STB                                | Latch input                  | Contents of data register are latched at rising edge, transferred to D/A converter, and output as analog voltage corresponding to display data. Contents of initial shift register are cleared after STB has been input. One pulse of this signal is input when $\mu$ PD16641 is started, and then device operates normally. For STB input timing, refer to Relations between STB, Start Pulse, and Blanking Period in Switching Characteristic Waveform. |

| V <sub>0</sub> to V <sub>10</sub>  | γ-corrected power supply     | Inputs $\gamma$ -corrected power from external source. $V_{SS2} \leq V_{10} \leq V_9 \leq V_8 \leq V_7 \leq V_6 \leq V_5 \leq V_4 \leq V_3 \leq V_2 \leq V_1 \leq V_0 \leq V_{DD2}$ $V_{SS2} \leq V_0 \leq V_1 \leq V_2 \leq V_3 \leq V_4 \leq V_5 \leq V_6 \leq V_7 \leq V_8 \leq V_9 \leq V_{10} \leq V_{DD2}$ Maintain gray scale power supply during gray scale voltage output.                                                                       |

| V <sub>DD1</sub>                   | Logic circuit power supply   | 3.3 V ± 0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD2</sub>                   | Driver circuit power supply  | $V_{sel}$ = $V_{DD2}$ or OPEN: $V_{DD2}$ = 3.3 V $\pm$ 0.3 V $V_{sel}$ = L : $V_{DD2}$ = 5.0 V $\pm$ 0.5 V                                                                                                                                                                                                                                                                                                                                                |

| Vss1                               | Logic ground                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Vss2                               | Driver ground                | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Caution Be sure to turn on power in the order V<sub>DD1</sub>, logic input, V<sub>DD2</sub>, and gray scale power (V<sub>0</sub> to V<sub>10</sub>), and turn off power in the reverse order, to prevent the μPD16641 from being damaged by latchup. Be sure to observe this power sequence even during a transition period.

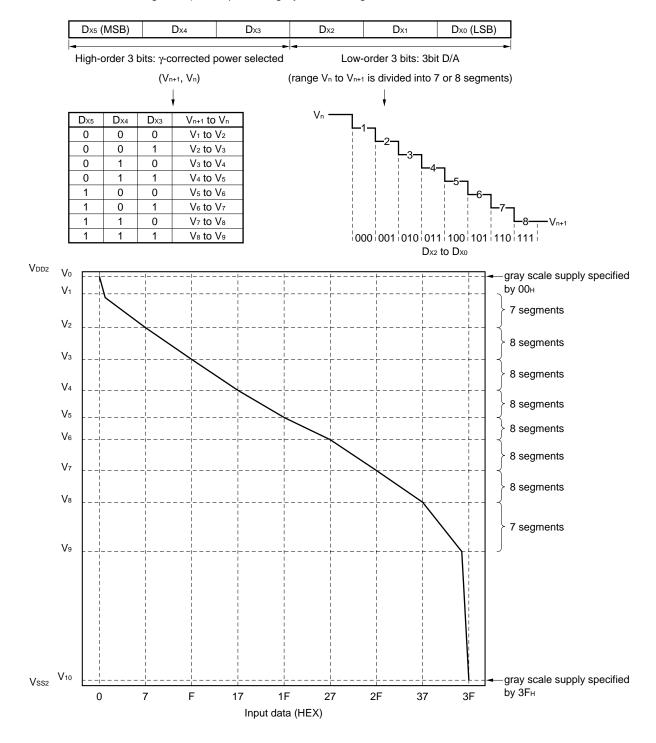

#### 4. RELATION BETWEEN INPUT DATA AND OUTPUT VOLTAGE VALUE

The 11 major points on the  $\gamma$  characteristic curve of the LCD panel are arbitrarily set by external power supplies V<sub>0</sub> through V<sub>10</sub>. If the display data is 00H or 3FH, gray scale voltage V<sub>0</sub> or V<sub>10</sub> is output. If the display data is in the range 01H to 3EH, the high-order 3 bits select an external powers pair V<sub>n+1</sub>, V<sub>n</sub>. The low-order 3 bits evenly divide the range of V<sub>n+1</sub> to V<sub>n</sub> into eight segments by means of D/A conversion (however, the ranges from V<sub>9</sub> to V<sub>8</sub> and from V<sub>2</sub> to V<sub>1</sub> are divided into seven segments) to output a 64 gray scale voltage.

## Relation between Input Data and Output Voltage

| Input Data      | D <sub>X5</sub> | D <sub>X4</sub> | Dхз | D <sub>X2</sub> | D <sub>X1</sub> | D <sub>X0</sub> | Output Voltage                 |

|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|--------------------------------|

| 00н             | 0               | 0               | 0   | 0               | 0               | 0               | V <sub>0</sub>                 |

| 01н             | 0               | 0               | 0   | 0               | 0               | 1               | $V_2 + (V_1 - V_2) \times 6/7$ |

| 02н             | 0               | 0               | 0   | 0               | 1               | 0               | $V_2 + (V_1 - V_2) \times 5/7$ |

| 03н             | 0               | 0               | 0   | 0               | 1               | 1               | $V_2 + (V_1 - V_2) \times 4/7$ |

| 04н             | 0               | 0               | 0   | 1               | 0               | 0               | $V_2 + (V_1 - V_2) \times 3/7$ |

| 05н             | 0               | 0               | 0   | 1               | 0               | 1               | $V_2 + (V_1 - V_2) \times 2/7$ |

| 06н             | 0               | 0               | 0   | 1               | 1               | 0               | $V_2 + (V_1 - V_2) \times 1/7$ |

| 07н             | 0               | 0               | 0   | 1               | 1               | 1               | V <sub>2</sub>                 |

| 08н             | 0               | 0               | 1   | 0               | 0               | 0               | $V_3 + (V_2 - V_3) \times 7/8$ |

| 09н             | 0               | 0               | 1   | 0               | Ö               | 1               | $V_3 + (V_2 - V_3) \times 6/8$ |

| ОАн             | 0               | 0               | 1   | 0               | 1               | 0               | $V_3 + (V_2 - V_3) \times 5/8$ |

| 0Вн             | Ö               | Ö               | 1   | Ö               | 1               | 1               | $V_3 + (V_2 - V_3) \times 4/8$ |

| 0Сн             | 0               | 0               | 1   | 1               | 0               | 0               | $V_3 + (V_2 - V_3) \times 3/8$ |

| ОДн             | 0               | 0               | 1   | 1               | 0               | 1               | $V_3 + (V_2 - V_3) \times 2/8$ |

| 0Ен             | 0               | 0               | 1   | 1               | 1               | 0               | $V_3 + (V_2 - V_3) \times 1/8$ |

| 0Fн             | 0               | 0               | 1   | 1               | 1               | 1               | V <sub>3</sub>                 |

| 10н             | 0               | 1               | 0   | 0               | 0               | 0               | $V_4 + (V_3 - V_4) \times 7/8$ |

| 11н             | 0               | 1               | 0   | 0               | 0               | 1               | $V_4 + (V_3 - V_4) \times 6/8$ |

| 12н             | Ö               | 1               | 0   | 0               | 1               | 0               | $V_4 + (V_3 - V_4) \times 5/8$ |

| 13н             | 0               | 1               | Ö   | 0               | 1               | 1               | $V_4 + (V_3 - V_4) \times 4/8$ |

| 14н             | 0               | 1               | 0   | 1               | 0               | 0               | $V_4 + (V_3 - V_4) \times 3/8$ |

| 15⊦             | 0               | 1               | 0   | 1               | 0               | 1               | $V_4 + (V_3 - V_4) \times 2/8$ |

| 16н             | 0               | 1               | 0   | 1               | 1               | 0               | $V_4 + (V_3 - V_4) \times 1/8$ |

| 17н             | 0               | 1               | 0   | 1               | 1               | 1               | V <sub>4</sub>                 |

| 18н             | 0               | 1               | 1   | 0               | 0               | 0               | $V_5 + (V_4 - V_5) \times 7/8$ |

| 19н             | Ö               | 1               | 1   | 0               | 0               | 1               | $V_5 + (V_4 - V_5) \times 6/8$ |

| 1Ан             | 0               | 1               | 1   | 0               | 1               | 0               | $V_5 + (V_4 - V_5) \times 5/8$ |

| 1Вн             | 0               | 1               | 1   | 0               | 1               | 1               | $V_5 + (V_4 - V_5) \times 4/8$ |

| 1Сн             | 0               | 1               | 1   | 1               | 0               | 0               | $V_5 + (V_4 - V_5) \times 3/8$ |

| 1Dн             | 0               | 1               | 1   | 1               | 0               | 1               | $V_5 + (V_4 - V_5) \times 2/8$ |

| 1Ен             | 0               | 1               | 1   | 1               | 1               | 0               | $V_5 + (V_4 - V_5) \times 1/8$ |

| <b>1</b> Fн     | 0               | 1               | 1   | 1               | 1               | 1               | V <sub>5</sub>                 |

| 20н             | 1               | 0               | 0   | 0               | 0               | 0               | $V_6 + (V_5 - V_6) \times 7/8$ |

| 21н             | 1               | 0               | 0   | 0               | 0               | 1               | $V_6 + (V_5 - V_6) \times 6/8$ |

| 22н             | 1               | 0               | 0   | 0               | 1               | 0               | $V_6 + (V_5 - V_6) \times 5/8$ |

| 23н             | 1               | 0               | 0   | 0               | 1               | 1               | $V_6 + (V_5 - V_6) \times 4/8$ |

| 24н             | 1               | 0               | 0   | 1               | 0               | 0               | $V_6 + (V_5 - V_6) \times 3/8$ |

| 25н             | 1               | 0               | 0   | 1               | 0               | 1               | $V_6 + (V_5 - V_6) \times 2/8$ |

| 26н             | 1               | 0               | 0   | 1               | 1               | 0               | $V_6 + (V_5 - V_6) \times 1/8$ |

| 27н             | 1               | 0               | 0   | 1               | 1               | 1               | V <sub>6</sub>                 |

| 28н             | 1               | 0               | 1   | 0               | 0               | 0               | $V_7 + (V_6 - V_7) \times 7/8$ |

| 29н             | 1               | 0               | 1   | 0               | 0               | 1               | $V_7 + (V_6 - V_7) \times 6/8$ |

| 2Ан             | 1               | 0               | 1   | 0               | 1               | 0               | $V_7 + (V_6 - V_7) \times 5/8$ |

| 2Вн             | 1               | 0               | 1   | 0               | 1               | 1               | $V_7 + (V_6 - V_7) \times 4/8$ |

| 2Сн             | 1               | 0               | 1   | 1               | 0               | 0               | $V_7 + (V_6 - V_7) \times 3/8$ |

| 2Dн             | 1               | 0               | 1   | 1               | 0               | 1               | $V_7 + (V_6 - V_7) \times 2/8$ |

| 2Ен             | 1               | 0               | 1   | 1               | 1               | 0               | $V_7 + (V_6 - V_7) \times 1/8$ |

| 2F <sub>H</sub> | 1               | 0               | 1   | 1               | 1               | 1               | V <sub>7</sub>                 |

| 30н             | 1               | 1               | 0   | 0               | 0               | 0               | $V_8 + (V_7 - V_8) \times 7/8$ |

| 31н             | 1               | 1               | 0   | 0               | 0               | 1               | $V_8 + (V_7 - V_8) \times 6/8$ |

| 32н             | 1               | 1               | 0   | 0               | 1               | 0               | $V_8 + (V_7 - V_8) \times 5/8$ |

| 33н             | 1               | 1               | 0   | 0               | 1               | 1               | $V_8 + (V_7 - V_8) \times 4/8$ |

| 34н             | 1               | 1               | 0   | 1               | 0               | 0               | $V_8 + (V_7 - V_8) \times 3/8$ |

| 35н             | 1               | 1               | 0   | 1               | 0               | 1               | $V_8 + (V_7 - V_8) \times 2/8$ |

| 36н             | 1               | 1               | 0   | 1               | 1               | 0               | $V_8 + (V_7 - V_8) \times 1/8$ |

| 37н             | 1               | 1               | 0   | 1               | 1               | 1               | V <sub>8</sub>                 |

| 38н             | 1               | 1               | 1   | 0               | 0               | 0               | $V_9 + (V_8 - V_9) \times 6/7$ |

| 39н             | 1               | 1               | 1   | 0               | 0               | 1               | $V_9 + (V_8 - V_9) \times 5/7$ |

| 3Ан             | 1               | 1               | 1   | 0               | 1               | 0               | $V_9 + (V_8 - V_9) \times 4/7$ |

| 3Вн             | 1               | 1               | 1   | 0               | 1               | 1               | $V_9 + (V_8 - V_9) \times 3/7$ |

| 3Сн             | 1               | 1               | 1   | 1               | 0               | 0               | $V_9 + (V_8 - V_9) \times 2/7$ |

| 3D <sub>H</sub> | 1               | 1               | 1   | 1               | 0               | 1               | $V_9 + (V_8 - V_9) \times 1/7$ |

| 3E <sub>H</sub> | 1               | 1               | 1   | 1               | 1               | 0               | V <sub>9</sub>                 |

| 3Fн             | 1               | 1               | 1   | 1               | 1               | 1               | V <sub>10</sub>                |

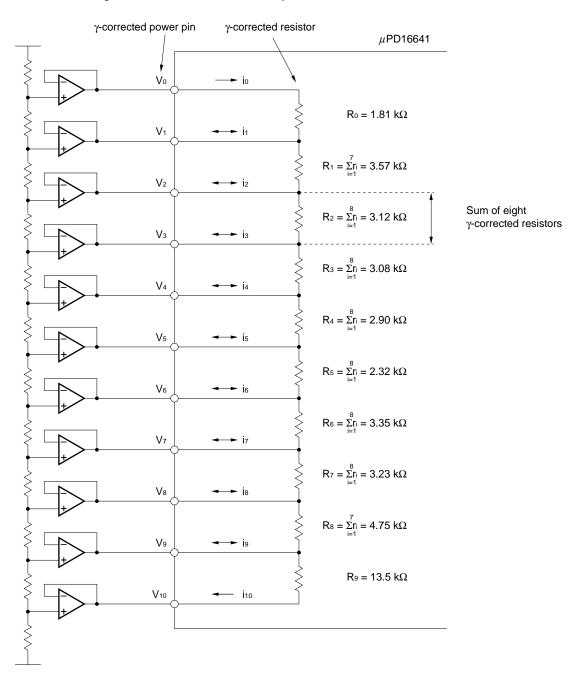

#### **γ**-Corrected Power Circuit

The reference power supply of the D/A converter consists of a ladder circuit with a total of 64 resistors, and resistance  $\Sigma$ ri between  $\gamma$ -corrected power pins differs depending on each pair of  $\gamma$ -corrected power pins. One pair of  $\gamma$ -corrected power pins consists of seven or eight series resistors, and resistance  $\Sigma$ ri in the figure below is indicated as the sum of the seven of eight resistors. The resistance ratio between the  $\gamma$ -corrected power pins ( $\Sigma$ ri ratio) is designed to be a value relatively close to the ratio of the  $\gamma$ -corrected voltages V<sub>1</sub> through V<sub>9</sub> (gray scale voltages in 8 steps) used in an actual LCD panel. Under ideal conditions where there is no difference between the two, therefore, there is no voltage difference between the voltage of the  $\gamma$ -corrected power supplies and the gray scale voltages in 8 steps of the resistor ladder circuits of the  $\gamma$ -corrected power supplies and the gray scale voltages in 8 steps of the resistor ladder circuits of the  $\gamma$ -corrected power pins V<sub>1</sub> through V<sub>9</sub>. As a result, a voltage follower circuit is not necessary.

#### **Relation between Input Data and Output Data**

Data format: 1 pixel data (6 bits) × RGB (3 dots)

Input width: 18 bits

$R/\overline{L} = H$  (right shift)

| Output | S <sub>1</sub>                     | S <sub>2</sub>                     | S <sub>3</sub>                     | <br>S239                               | S <sub>240</sub>                   |

|--------|------------------------------------|------------------------------------|------------------------------------|----------------------------------------|------------------------------------|

| Data   | D <sub>00</sub> to D <sub>05</sub> | D <sub>10</sub> to D <sub>15</sub> | D <sub>20</sub> to D <sub>25</sub> | <br>D <sub>10</sub> to D <sub>15</sub> | D <sub>20</sub> to D <sub>25</sub> |

$R/\overline{L} = L$  (left shift)

| Output | S <sub>1</sub>                     | S <sub>2</sub>                     | S₃                                 | <br>S239                               | S <sub>240</sub>                   |

|--------|------------------------------------|------------------------------------|------------------------------------|----------------------------------------|------------------------------------|

| Data   | D <sub>00</sub> to D <sub>05</sub> | D <sub>10</sub> to D <sub>15</sub> | D <sub>20</sub> to D <sub>25</sub> | <br>D <sub>10</sub> to D <sub>15</sub> | D <sub>20</sub> to D <sub>25</sub> |

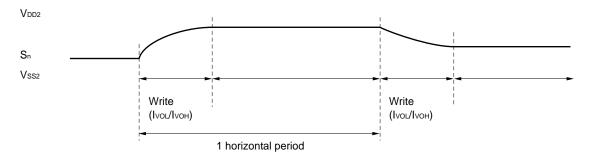

#### 5. OPERATION OF OUTPUT BUFFER

The output buffer consists of an operational amplifier circuit that does not perform precharge operation. Therefore, driver output current IVOH1/2 is the charging current to the LCD, and IVOL1/2 is the discharging current.

The chip has the driving capability to charge or discharge a liquid load with  $C_L = 80$  pF to  $3 \tau$  in less than 10  $\mu$ s.

#### <LCD panel driving waveform of μPD16641>

## 6. ELECTRIC SPECIFICATION

# Absolute Maximum Ratings (Vss1 = Vss2 = 0 V)

| Parameter                   | Symbol            | Rating                            | Unit |

|-----------------------------|-------------------|-----------------------------------|------|

| Supply voltage              | V <sub>DD1</sub>  | -0.3 to +4.5                      | V    |

| Supply voltage              | V <sub>DD2</sub>  | -0.3 to +7.0                      | V    |

| Input voltage               | Vı                | -0.3 to V <sub>DD1, 2</sub> + 0.3 | V    |

| Output voltage              | Vo                | -0.3 to V <sub>DD1, 2</sub> + 0.3 | V    |

| Permissible dissipation     | P□                | 150                               | mW   |

| Operating temperature range | TA                | -10 to +75                        | °C   |

| Storage temperature range   | T <sub>stg.</sub> | -55 to +125                       | °C   |

# Recommended Operating Range (T<sub>A</sub> = -10 to +75°C, Vss1 = Vss2 = 0 V)

| Parameter               | Symbol                            | Condition            | MIN.       | TYP. | MAX.                   | Unit |

|-------------------------|-----------------------------------|----------------------|------------|------|------------------------|------|

| Logic supply voltage    | V <sub>DD1</sub>                  |                      | 3.0        | 3.3  | 3.6                    | V    |

| Driver supply voltage   | V <sub>DD2</sub>                  | V <sub>sel</sub> = H | 3.0        | 3.3  | 3.6                    | V    |

| Driver supply voltage   | V <sub>DD2</sub>                  | V <sub>sel</sub> = L | 4.5        | 5.0  | 5.5                    | V    |

| γ-corrected power       | V <sub>0</sub> to V <sub>10</sub> |                      | Vss2 + 0.1 |      | V <sub>DD2</sub> – 0.1 | V    |

| Maximum clock frequency | f <sub>max</sub> .                |                      | 33         |      |                        | MHz  |

| Output load capacitance | C∟                                |                      |            |      | 150                    | рF   |

## Electrical Characteristics ( $T_A = -10 \text{ to } +75^{\circ}\text{C}$ , $V_{DD1} = 3.0 \text{ to } 3.6 \text{ V}$ , $V_{DD2} = 3.0 \text{ to } 3.6 \text{ V}$ or 4.5 to 5.5 V, $V_{SS1} = V_{SS2} = 0 \text{ V}$ )

| Parameter                                            | Symbol           | Condition                                                                                            |                 | MIN.                   | TYP. | MAX.                | Unit |

|------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|-----------------|------------------------|------|---------------------|------|

| High-level input voltage                             | ViH              | R/L, CLK, STB, STHR (L),                                                                             |                 | 0.7V <sub>DD1</sub>    |      | V <sub>DD1</sub>    | V    |

| Low-level input voltage                              | VIL              | D00-05, D10-15, D20-25                                                                               |                 | 0                      |      | 0.3V <sub>DD1</sub> | V    |

| Input leakage current                                | lι               | D <sub>00-05</sub> , D <sub>10-15</sub> , D <sub>20-25</sub><br>R/L, CLK, STB, STHR (L)              | <b>–</b> ' '    |                        |      | ±1.0                | μΑ   |

| Pull-up resistor                                     | Rpu              | Vsel, VDD2 = 5.0 V, Vsel, = 0 V                                                                      |                 | 40                     | 100  | 250                 | kΩ   |

| High-level output voltage                            | Vон              | STHR (L), Io = -1.0 mA                                                                               |                 | V <sub>DD1</sub> - 0.5 |      |                     | V    |

| Low-level output voltage                             | Vol              | STHR (L), Io = +1.0 mA                                                                               |                 |                        |      | 0.5                 | V    |

| Static current consumption of                        | I <sub>Vn1</sub> | V <sub>DD1</sub> = 3.3 V, V <sub>DD2</sub> = 3.3 V                                                   | V <sub>10</sub> | -200                   | -150 |                     | μΑ   |

| $\gamma$ -corrected power (V <sub>DD2</sub> = 3.3 V) |                  | $V_0 = 3.20 \text{ V}, V_6 = 1.95 \text{ V}$<br>$V_1 = 3.07 \text{ V}, V_7 = 1.70 \text{ V}$         | V <sub>9</sub>  |                        | ±10  |                     | μΑ   |

|                                                      |                  | V <sub>2</sub> = 2.80 V, V <sub>8</sub> = 1.46 V                                                     | to              |                        |      |                     |      |

|                                                      |                  | $V_3 = 2.57 \text{ V}, V_9 = 1.11 \text{ V}$<br>$V_4 = 2.34 \text{ V}, V_{10} = 0.10 \text{ V}$      | V <sub>1</sub>  |                        |      |                     |      |

|                                                      |                  | V <sub>5</sub> = 2.12 V, Note                                                                        | Vo              |                        | 150  | 200                 | μΑ   |

| Static current consumption of                        | I <sub>Vn2</sub> | V <sub>DD1</sub> = 3.3 V, V <sub>DD2</sub> = 5.0 V                                                   | V <sub>10</sub> | -300                   | -250 |                     | μΑ   |

| $\gamma$ -corrected power (V <sub>DD2</sub> = 5.0 V) |                  | $V_0 = 4.90 \text{ V}, V_6 = 2.96 \text{ V}$<br>$V_1 = 4.69 \text{ V}, V_7 = 2.58 \text{ V}$         | V <sub>9</sub>  |                        | ±10  |                     | μΑ   |

|                                                      |                  | V <sub>2</sub> = 4.28 V, V <sub>8</sub> = 2.20 V                                                     | to              |                        |      |                     |      |

|                                                      |                  | V <sub>3</sub> = 3.92 V, V <sub>9</sub> = 1.66 V<br>V <sub>4</sub> = 3.56 V, V <sub>10</sub> = 0.1 V | V <sub>1</sub>  |                        |      |                     |      |

|                                                      |                  | V <sub>5</sub> = 3.23 V, Note                                                                        | Vo              |                        | 250  | 300                 | μΑ   |

(Vx is output voltage of analog output pin S1 to S240. VouT is the voltage applied to analog output pin S1 to S240.)

**Note** Apply ideal voltage to V<sub>1</sub> to V<sub>9</sub> that is calculated from internal resistor.

## Electrical Characteristics (TA = -10 to +75°C, VDD1 = 3.0 to 3.6 V, VDD2 = 3.0 to 3.6 V or 4.5 to 5.5 V, VSS1 = VSS2 = 0 V)

| Parameter                            | Symbol            | Condition                                                                       | MIN.       | TYP. | MAX.                   | Unit |

|--------------------------------------|-------------------|---------------------------------------------------------------------------------|------------|------|------------------------|------|

| Driver output current (VDD2 = 3.3 V) | Ivoн1             | STB = 3.3 V<br>Vout = 2.2 V, Vx = 3.2 V<br>VDD1 = VDD2 = 3.3 V                  |            | -0.3 | -0.075                 | mA   |

|                                      | Ivol1             | STB = 3.3 V<br>Vout = 1.1 V, Vx = 0.1 V<br>VDD1 = VDD2 = 3.3 V                  | 0.075      | 0.25 |                        | mA   |

| Driver output current (VDD2 = 5.0 V) | Ivoн2             | STB = 5.0 V<br>Vout = 3.9 V, Vx = 4.9 V<br>VDD1 = 3.3 V, VDD2 = 5.0 V           |            | -0.3 | -0.1                   | mA   |

|                                      | Ivol2             | STB = 5.0 V<br>Vout = 1.1 V, Vx = 0.1 V<br>VDD1 = 3.3 V, VDD2 = 5.0 V           | 0.1        | 0.25 |                        | mA   |

| Output voltage deviation             | ΔVo               | V <sub>DD1</sub> = 3.3 V, V <sub>DD2</sub> = 3.3 V<br>V <sub>OUT</sub> = 1.65   |            | ±20  | ±25                    | mV   |

|                                      |                   | V <sub>DD1</sub> = 3.3 V, V <sub>DD2</sub> = 5.0 V<br>V <sub>OUT</sub> = 2.50 V |            | ±20  | ±25                    | mV   |

| Output voltage range                 | Vo                | Input data: 00н to 3Fн                                                          | Vss2 + 0.1 |      | V <sub>DD2</sub> - 0.1 | V    |

| Dynamic logic current consumption    | I <sub>DD1</sub>  | No load <sup>Note</sup>                                                         |            |      | 2.0                    | mA   |

| Dynamic driver current consumption   | I <sub>DD21</sub> | No load, $V_{DD2}$ = 3.3 V $\pm$ 0.3 V <sup>Note</sup>                          |            |      | 5.0                    | mA   |

| Dynamic driver current consumption   | I <sub>DD22</sub> | No load, $V_{DD2} = 5.0 \text{ V} \pm 0.5 \text{ V}^{\text{Note}}$              |            |      | 6.5                    | mA   |

**Note** The STB cycle is specified at 31  $\mu$ s and fcLk = 16 MHz. Input data: 1010... (checkerboard pattern) Refers to current consumption per driver when cascades are connected under the assumption of VGA single-sided mounting (8 units).

# Switching Characteristics (TA = -10 to +75°C, VDD1 = 3.0 to 3.6 V, VDD2 = 3.0 to 3.6 V or 4.5 to 5.5 V, VSS1 = VSS2 = 0 V, tr = tf = 3.0 ns)

| Parameter                  | Symbol            | Con                             | dition                                        | MIN. | TYP. | MAX. | Unit |

|----------------------------|-------------------|---------------------------------|-----------------------------------------------|------|------|------|------|

| Start pulse delay time     | t <sub>PLH1</sub> | C <sub>L</sub> = 15 pF          |                                               | 2.0  |      | 17   | ns   |

| Start pulse delay time     | t <sub>PHL1</sub> | C∟ = 15 pF                      |                                               | 2.0  |      | 17   | ns   |

| Driver output delay time 1 | <b>t</b> PLH21    | V <sub>DD2</sub> = 3.3 V        | Vo: $0.1 \text{ V} \rightarrow 3.2 \text{ V}$ |      | 6.0  | 12   | μs   |

| Driver output delay time 2 | <b>t</b> PLH31    | $2 k\Omega + 75 pF \times 2$    |                                               |      | 8.0  | 14   | μs   |

| Driver output delay time 1 | <b>t</b> PHL21    |                                 | Vo: 3.2 V → 0.1 V                             |      | 6.0  | 10   | μs   |

| Driver output delay time 2 | <b>t</b> PHL31    |                                 |                                               |      | 8.0  | 12   | μs   |

| Driver output delay time 1 | <b>t</b> PLH22    | V <sub>DD2</sub> = 5.0 V        | Vo: $0.1 \text{ V} \rightarrow 4.9 \text{ V}$ |      | 6.0  | 10   | μs   |

| Driver output delay time 2 | <b>t</b> PLH32    | $2 k\Omega + 75 pF \times 2$    |                                               |      | 8.0  | 12   | μs   |

| Driver output delay time 1 | <b>t</b> PHL22    |                                 | Vo: 4.9 V → 0.1 V                             |      | 6.0  | 8.0  | μs   |

| Driver output delay time 2 | <b>t</b> PHL32    |                                 |                                               |      | 8.0  | 10   | μs   |

| Input capacitance          | Cıı               | Vo to V10, TA = 25°C            |                                               |      | 100  |      | pF   |

| Input capacitance          | C <sub>12</sub>   | STHR (L), T <sub>A</sub> = 25°C |                                               |      | 10   | 15   | pF   |

| Input capacitance          | Сіз               | STHR (L), other to              | han Vo to V10                                 |      | 7.0  | 10   | pF   |

# Timing Requirements (T<sub>A</sub> = -10 to +75°C, V<sub>DD1</sub> = 3.0 to 3.6 V, V<sub>DD2</sub> = 3.0 to 3.6 V or 4.5 to 5.5 V, V<sub>SS1</sub> = V<sub>SS2</sub> = 0 V, t<sub>r</sub> = t<sub>f</sub> = 3.0 ns)

| Parameter              | Symbol       | Condition                                                 | MIN. | TYP. | MAX. | Unit |

|------------------------|--------------|-----------------------------------------------------------|------|------|------|------|

| Clock pulse width      | PWclk        |                                                           | 22   |      |      | ns   |

| Clock low period       | PWclk(L)     |                                                           | 4.0  |      |      | ns   |

| Clock high period      | PWclk(H)     |                                                           | 4.0  |      |      | ns   |

| Data setup time        | tsetup1      |                                                           | 2.0  |      |      | ns   |

| Data hold time         | tHOLD1       |                                                           | 2.0  |      |      | ns   |

| Start pulse setup time | tsetup2      |                                                           | 2.0  |      |      | ns   |

| Start pulse hold time  | tHOLD2       |                                                           | 2.0  |      |      | ns   |

| Start pulse low period | tspl         |                                                           | 2    |      |      | CLK  |

| Start pulse rise time  | tspr         |                                                           |      | 80   |      | CLK  |

| STB setup time         | tsetup3      |                                                           | 1    |      |      | CLK  |

| Data invalid period    | tinv         |                                                           |      | 1    |      | CLK  |

| Final data timing      | <b>t</b> LDT |                                                           |      |      | 1    | CLK  |

| CLK-STB time           | tclk-sтв     | $CLK \uparrow \to STB \uparrow or \downarrow$             | 7.0  |      |      | ns   |

| STB-CLK time           | tsтв-clк     | STB $\uparrow$ or $\downarrow \rightarrow$ CLK $\uparrow$ | 7.0  |      |      | ns   |

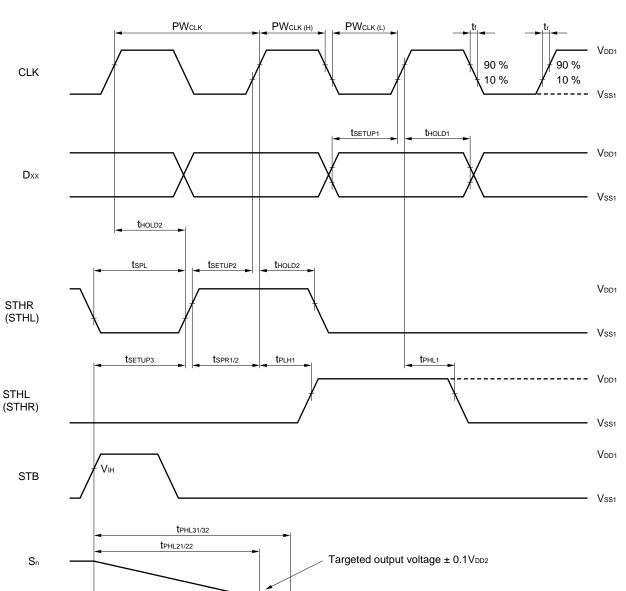

# 7. SWITCHING CHARACTERISTIC WAVEFORM $(R/\overline{L} = H)$

tPHL31/32

$S_n$

The figures in parenthesis indicate R/L = L

Unless otherwise specified, the input level is VIH = 0.7 VDD1, VIL = 0.3 VDD1.

Targeted output voltage ± 0.1V<sub>DD2</sub>

Targeted output voltage (6-bit accuracy)

#### **Switching Characteristic Waveform**

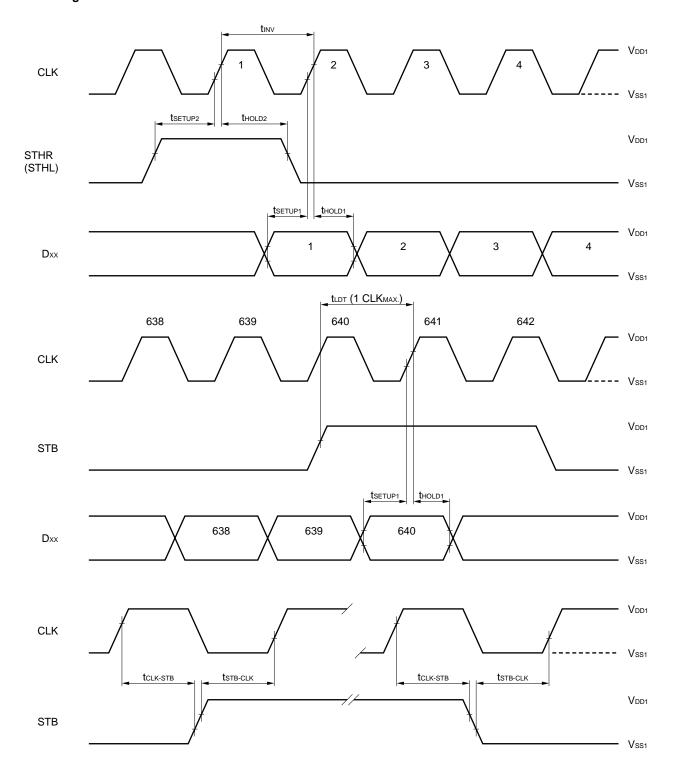

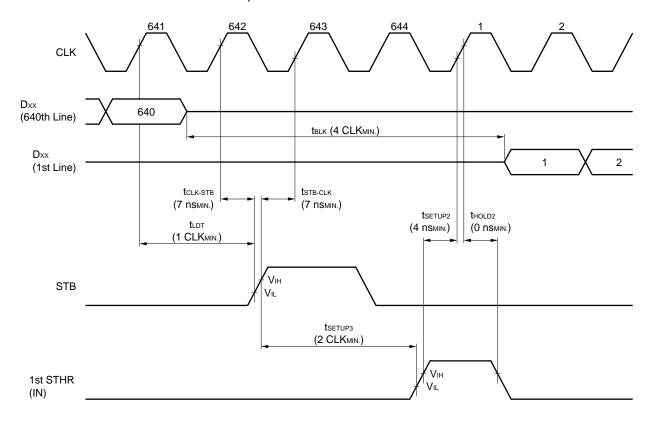

# 8. RELATION BETWEEN STB/STHR, STHL AND BLANKING PERIOD

## 9. DATA INPUT TIMING IN CASCADE CONNECTION

#### 10. RECOMMENDED MOUNTING CONDITIONS

Mounting this product under the following conditions is recommended. For the mounting methods and conditions other than those recommended, consult NEC.

| Mounting Conditions       | Mounting Method      | Conditions                                                                                                                                                                                                     |

|---------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermocompression bonding | Soldering            | Heating tool: 300 to 350°C, Heating time: 2 to 3 seconds, Pressure: 100 g (per product)                                                                                                                        |

|                           | ACF (sheet adhesive) | Preliminary adhesion: 70 to 100°C, Pressure: 3 to 8 kg/cm², Time: 3 to 5 seconds Real adhesion: 165 to 180°C, Pressure: 25 to 45 kg/cm², Time 30 to 40 seconds (when SUMIZAC1003 of Sumitomo Bakelite is used) |

$\textbf{Note} \quad \text{For the mounting conditions for ACF, consult the ACF manufacturer.}$

Do not use two or more mounting methods in combination.

#### Reference

NEC Semiconductor Device Reliability/Quality Control System (C10983E)

Quality Grades to NEC's Semiconductor Devices (C11531E)

[MEMO]

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.